APPLICATION NOTE PMC-990715 PMC-Sierra, Inc.

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

**PM7384**

## FREEDM<sup>TM</sup>-84P672

# FRAME ENGINE AND DATALINK MANAGER 84P672

# **PROGRAMMER'S GUIDE**

PROPRIETARY AND CONFIDENTIAL ADVANCE ISSUE 1: JUNE 1999

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

APPLICATION NOTE PMC-990715 PMC-Sierra, Inc.

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

## **CONTENTS**

| 1 |      |                                           |  |  |

|---|------|-------------------------------------------|--|--|

|   | 1.1  | SCOPE1                                    |  |  |

|   | 1.2  | TARGET AUDIENCE1                          |  |  |

|   | 1.3  | NUMBERING CONVENTIONS1                    |  |  |

|   | 1.4  | REGISTER DESCRIPTION1                     |  |  |

|   |      | 1.4.1 NORMAL MODE REGISTERS2              |  |  |

|   |      | 1.4.2 PCI CONFIGURATION REGISTERS2        |  |  |

| 2 | REFE | RENCES4                                   |  |  |

| 3 | FREE | DM-84P672 OVERVIEW5                       |  |  |

|   | 3.1  | FREEDM-84P672 SUMMARY5                    |  |  |

|   | 3.2  | PCI INTERFACE                             |  |  |

| 4 | DATA | STRUCTURES                                |  |  |

|   | 4.1  | DESCRIPTOR TABLE10                        |  |  |

|   | 4.2  | RECEIVE PACKET DESCRIPTOR 11              |  |  |

|   | 4.3  | TRANSMIT DESCRIPTOR15                     |  |  |

|   | 4.4  | DATA BUFFERS                              |  |  |

|   | 4.5  | REFERENCES                                |  |  |

|   |      | 4.5.1 RECEIVE PACKET DESCRIPTOR REFERENCE |  |  |

|   |      | 4.5.2 TRANSMIT DESCRIPTOR REFERENCE       |  |  |

|   |      | 4.5.3 ACCESS TO DESCRIPTORS               |  |  |

|   | 4.6  | QUEUES23                                  |  |  |

| 5 | INTE | RRUPT ARCHITECTURE35                      |  |  |

APPLICATION NOTE PMC-990715

| 990715 |       | ISSUE 1                                            | PROGRAMMER'S GUIDE |

|--------|-------|----------------------------------------------------|--------------------|

|        | 5.1   | NON-SBI INTERRUPTS                                 |                    |

|        | 5.2   | SBI INTERRUPTS                                     | 37                 |

| 6      | PCI C | ONFIGURATION SPACE                                 |                    |

|        | 6.1   | ACCESSING THE PCI CONFIGURATION SPACE              |                    |

|        | 6.2   | PCI CONFIGURATION REGISTERS                        |                    |

| 7      | CON   | FIGURING THE SBI INTERFACE                         | 41                 |

|        | 7.1   | CONFIGURING THE SBI DROP BUS                       | 41                 |

|        | 7.2   | CONFIGURING THE SBI ADD BUS                        | 42                 |

| 8      | CON   | FIGURING THE SBI EXTRACTER AND INSERTER            | 45                 |

|        | 8.1   | CONFIGURING THE SBI EXTRACTER                      | 45                 |

|        |       | 8.1.1 SBI EXTRACT CONTROL                          | 45                 |

|        |       | 8.1.2 SBI EXTRACT TRIBUTARY CONFIGURAT             | ION46              |

|        | 8.2   | CONFIGURING THE SBI INSERTER                       | 48                 |

|        |       | 8.2.1 SBI INSERT CONTROL                           | 48                 |

|        |       | 8.2.2 SBI INSERT TRIBUTARY CONFIGURATIO            | N49                |

| 9      | CON   | FIGURING THE SERIAL LINKS                          | 51                 |

|        | 9.1   | SBI SPE/TRIBUTARY LINKS                            | 55                 |

|        | 9.2   | CLOCK/DATA LINKS                                   | 57                 |

| 10     | CON   | FIGURING THE PCI INTERFACE                         | 60                 |

|        | 10.1  | CONFIGURING THE RECEIVE DMA CONTROLL               |                    |

|        | 10.2  | CONFIGURING THE TRANSMIT DMA CONTROL               | · · · · ·          |

|        | 10.3  | CONFIGURING THE GENERAL-PURPOSE PCI (<br>(GPIC672) |                    |

PM7384 FREEDM-84P672

| APPLICATION NOTE<br>PMC-990715 |       | •        | ISSUE 1                                                | PROGRAMMER'S GUIDE |

|--------------------------------|-------|----------|--------------------------------------------------------|--------------------|

| 11                             | HDLC  | AND CH   | ANNEL FIFO CONFIGURATION                               |                    |

|                                | 11.1  | CONFIG   | SURING THE RHDL672                                     | 68                 |

|                                | 11.2  | CONFIG   | GURING THE THDL672                                     | 69                 |

|                                | 11.3  | PROGR    | AMMING A CHANNEL FIFO                                  | 71                 |

|                                |       | 11.3.1 R | ECEIVE CHANNEL FIFO                                    | 71                 |

|                                |       | 11.3.2 T | RANSMIT CHANNEL FIFO                                   | 72                 |

|                                | 11.4  | RHDL67   | 72 CHANNEL CONFIGURATION                               | 73                 |

|                                | 11.5  | THDL67   | 2 CHANNEL CONFIGURATION                                | 76                 |

| 12                             | FREE  | DM-84P6  | 672 OPERATIONAL PROCEDURES                             | 83                 |

|                                | 12.1  |          | E IDENTIFICATION, LOCATION AND SYSTE<br>RCE ASSIGNMENT |                    |

|                                | 12.2  | RESET.   |                                                        | 85                 |

|                                | 12.3  | INITIALI | ZATION                                                 | 85                 |

|                                | 12.4  | ACTIVA   | TION PROCEDURE                                         |                    |

|                                | 12.5  | DEACTI   | VATION PROCEDURE                                       | 87                 |

|                                | 12.6  | PROVIS   | BIONING A CHANNEL                                      | 87                 |

|                                |       | 12.6.1 R | ECEIVE CHANNEL PROVISIONING                            | 87                 |

|                                |       | 12.6.2 T | RANSMIT CHANNEL PROVISIONING                           | 90                 |

|                                | 12.7  | UNPRO    | VISIONING A CHANNEL                                    | 92                 |

|                                |       | 12.7.1 R | ECEIVE CHANNEL UNPROVISIONING                          | 92                 |

|                                |       | 12.7.2 T | RANSMIT CHANNEL UNPROVISIONING                         | 96                 |

|                                | 12.8  | RECEIV   | E SEQUENCE                                             |                    |

|                                | 12.9  | TRANS    | MIT SEQUENCE                                           | 100                |

|                                | 12.10 | PERFO    | RMANCE COUNTERS                                        | 102                |

ADVANCE APPLICATION NOTE PMC-990715

ISSUE 1

PROGRAMMER'S GUIDE

| 12.11 LINE LOOPBACK                                   |

|-------------------------------------------------------|

| 12.12 DIAGNOSTIC LOOPBACK                             |

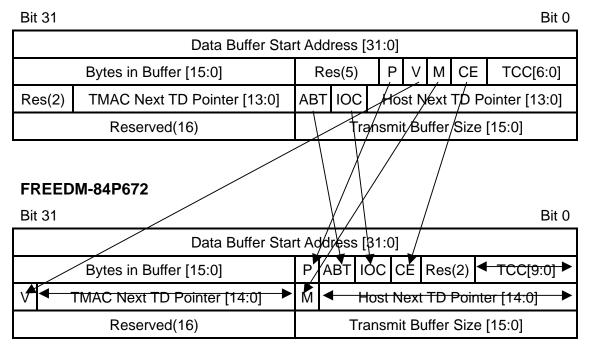

| APPENDIX A – RECEIVE PACKET DESCRIPTOR CHANGES106     |

| APPENDIX B – TRANSMIT DESCRIPTOR CHANGES107           |

| APPENDIX C – REGISTER LEVEL CHANGES108                |

| APPENDIX D – NEW NORMAL MODE REGISTERS                |

| APPENDIX E – NON-APPLICABLE NORMAL MODE REGISTERS 119 |

| APPENDIX F – MOVED NORMAL MODE REGISTERS              |

| APPENDIX G – NORMAL MODE REGISTER BIT CHANGES         |

| APPENDIX H – PCI CONFIGURATION REGISTER BIT CHANGES   |

APPLICATION NOTE PMC-990715 PMC-Sierra, Inc.

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

## LIST OF FIGURES

| FIGURE 1 – FREEDM-84P672 BLOCK DIAGRAM6                       |

|---------------------------------------------------------------|

| FIGURE 2 – PCI ADDRESS MAP8                                   |

| FIGURE 3 – DATA STRUCTURE RELATIONSHIPS10                     |

| FIGURE 4 – RECEIVE PACKET DESCRIPTOR12                        |

| FIGURE 5 – TRANSMIT DESCRIPTOR15                              |

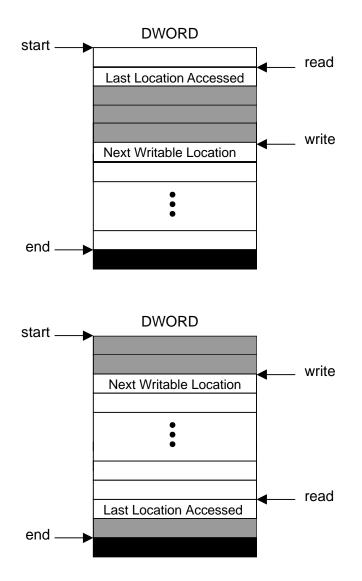

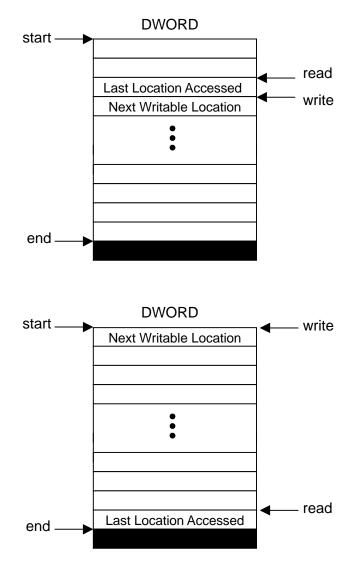

| FIGURE 6 – NORMAL QUEUE STATES                                |

| FIGURE 7 – EMPTY QUEUE STATES27                               |

| FIGURE 8 – FULL QUEUE STATES                                  |

| FIGURE 9 – FREEDM-84P672 TYPE 0 CONFIGURATION SPACE HEADER 40 |

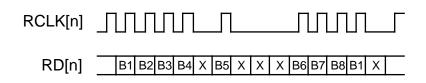

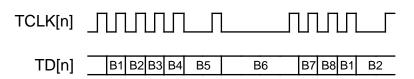

| FIGURE 10 – RECEIVE LINK TIMING58                             |

| FIGURE 11 – TRANSMIT LINK TIMING58                            |

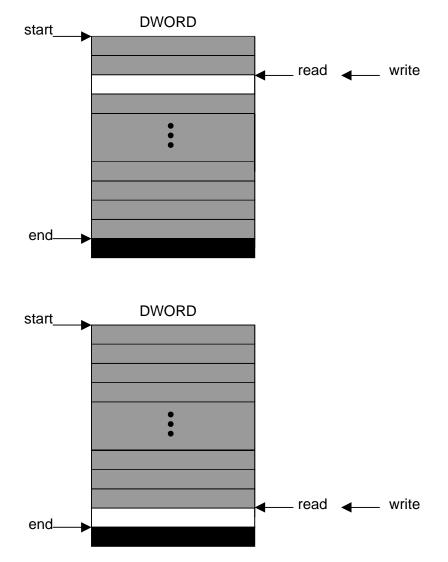

| FIGURE 12 – LITTLE ENDIAN FORMAT66                            |

| FIGURE 13 – BIG ENDIAN FORMAT66                               |

| FIGURE 14 – SPECIFYING A CHANNEL FIFO71                       |

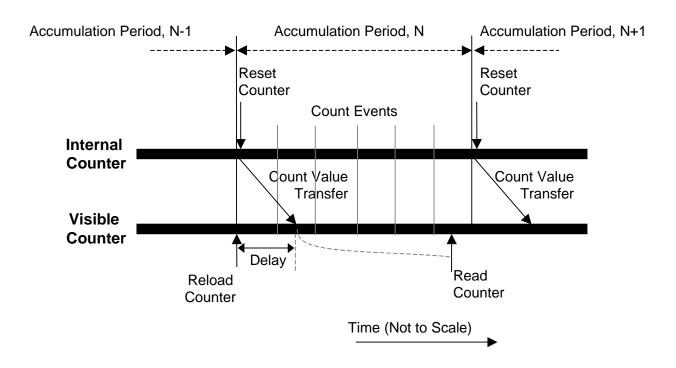

| FIGURE 15 – EVENT SEQUENCE FOR POLLING OF COUNTERS102         |

| FIGURE 16 – LINE LOOPBACK                                     |

| FIGURE 17 – DIAGNOSTIC LOOPBACK105                            |

| FIGURE 18 – CHANGES TO RECEIVE PACKET DESCRIPTOR 106          |

| FIGURE 19 – CHANGES TO TRANSMIT DESCRIPTOR                    |

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

#### 1 INTRODUCTION

#### 1.1 Scope

The FREEDM-84P672 Programmer's Guide describes the configurable features and operation of a FREEDM-84P672 from a programmer's perspective. This document may not cover all applications of the FREEDM-84P672. Please contact a PMC-Sierra Applications Engineer for specific uses not covered in this document.

This document is a supplement to the FREEDM-84P672 Longform Datasheet[1]. Both documents should be studied together to interface the FREEDM-84P672 to an embedded processor. In case of a discrepancy between the Programmer's Guide and the Longform Datasheet, the Longform Datasheet shall always be considered correct.

#### 1.2 Target Audience

The FREEDM-84P672 Programmer's Guide describes the data structures and initialisation necessary for programming the FREEDM-84P672 from a programmer's perspective. This document has been prepared for readers with prior knowledge of the HDLC protocol.

Although the examples provided in this document are described in C language syntax, they are not meant as compile-ready code segments.

## **1.3 Numbering Conventions**

The following numbering conventions are used throughout this document:

| binary      | 011 1010B, 011 |

|-------------|----------------|

| decimal     | 129, 6, 12     |

| hexadecimal | 0x1FE2, 09FH   |

## 1.4 Register Description

Unless specified, FREEDM-84P672 registers are described using the convention **REGISTER\_NAME** (byte offset from base address). There are two register spaces that can be addressed on a FREEDM-84P672 – they are the normal mode registers and the PCI configuration registers.

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

### **1.4.1 Normal Mode Registers**

Normal mode registers are used to configure, monitor and control the operation of the FREEDM-84P672. Registers must be accessed as 32-bit values with a dword aligned address. A register value is accessed through the PCI Host interface during a PCI bus read, or write transaction, and has the following characteristics:

- Writing values into unused register bits has no effect. However, to ensure software compatibility with future, feature-enhanced versions of the product, unused register bits should be written with logic zero. Reading back unused bits can produce either a logic one or a logic zero; hence, unused register bits should be masked off by software during a register read access.

- Except where noted, all configuration bits that can be written into can also be read back. This allows the processor controlling the FREEDM-84P672 to determine the programming state of the block.

- Writable normal mode registers are cleared to logic zero upon reset unless otherwise noted.

- Writing into read-only normal mode register bit locations does not affect FREEDM-84P672 operation unless otherwise noted.

- Certain register bits are reserved. These bits are associated with megacell functions that are unused in this application. To ensure that the FREEDM-84P672 operates as intended, reserved register bits must only be written with their default values. Similarly, writing to reserved registers should be avoided.

## 1.4.2 PCI Configuration Registers

PCI configuration registers are defined by the PCI SIG[2] and are used to install and configure devices on the PCI bus. Registers must be accessed as 32-bit values with a dword aligned address. A register value is only accessed through the PCI Host interface during a PCI configuration cycle, and has the following characteristics:

Writing values into unused register bits has no effect. However, to ensure software compatibility with future, feature-enhanced versions of the product, unused register bits must be written with logic zero. Reading back unused bits can produce either a logic one or a logic zero; hence unused register bits should be masked off by software when read. ADVANCE APPLICATION NOTE

PMC-990715

PROGRAMMER'S GUIDE

- Except where noted, all configuration bits that can be written into can also be read back. This allows the processor controlling the FREEDM-84P672 to determine the programming state of the block.

- Writable PCI configuration register bits are cleared to logic zero upon reset unless otherwise noted.

- Writing into read-only PCI configuration register bit locations does not affect FREEDM-84P672 operation unless otherwise noted.

- Certain register bits are reserved. These bits are associated with megacell functions that are unused in this application. To ensure that the FREEDM-84P672 operates as intended, reserved register bits must only be written with their default values. Similarly, writing to reserved registers should be avoided.

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

### 2 REFERENCES

- 1. PMC-990445, PMC-Sierra, Inc., "Frame Engine and Data Link Manager 84P672" Longform Datasheet, April 1999, Issue 1.

- 2. PCI Special Interest Group, PCI Local Bus Specification, June 1, 1995, Version 2.1.

- 3. PMC-960758, PMC-Sierra, Inc., "Frame Engine and Data Link Manager" Longform Datasheet, May 1998, Issue 5.

- 4. PMC-980577, PMC-Sierra, Inc., "Saturn Compatible Scaleable Bandwidth Interconnect (SBI) Specification", October 1998, Issue 3.

- 5. PMC-990262, PMC-Sierra, Inc., "Frame Engine and Data Link Manager 32P672" Longform Datasheet, May 1999, Issue 2.

APPLICATION NOTE PMC-990715

ISSUE 1

PM7384 FREEDM-84P672

PROGRAMMER'S GUIDE

## 3 FREEDM-84P672 OVERVIEW

#### 3.1 FREEDM-84P672 Summary

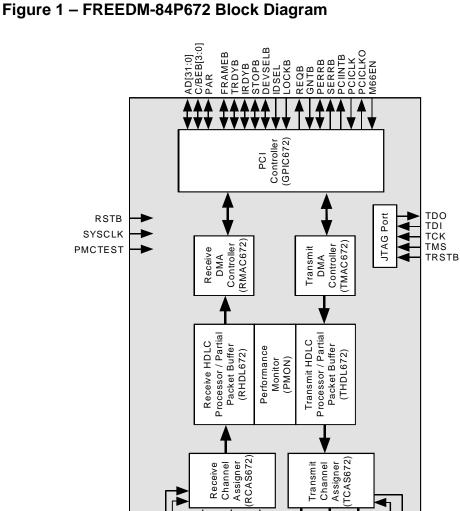

The PM7384 FREEDM-84P672 Frame Engine and Datalink Manager is an advanced data link layer processor that is ideal for applications such as IETF PPP interfaces for routers, Frame Relay switches and multiplexors, ATM switches and multiplexors, Internet/Intranet access equipment, packet-based DSLAM equipment, Packet over SONET, and PPP over SONET. The FREEDM-84P672 implements HDLC processing and PCI Bus memory management functions for a maximum of 672 bi-directional channels. The functional blocks of the FREEDM-84P672 are illustrated in Figure 1.

The FREEDM-84P672 may be configured to support channelised T1/J1/E1 or unchannelised DS-3 traffic on up to 84 links conveyed via a Scaleable Bandwidth Interconnect (SBI) interface. The SBI interface transports data in three Synchronous Payload Envelopes (SPEs), each of which may be configured independently to carry either 28 T1/J1 links, 21 E1 links or a single DS-3 link.

For channelised T1/J1/E1 links, the FREEDM-84P672 allows up to 672 bidirectional HDLC channels to be assigned to individual time-slots within each independently timed T1/J1 or E1 link. These links are processed by the Receive Channel Assigner (RCAS672) and the Transmit Channel Assigner (TCAS672). The channel assignment supports the concatenation of time-slots (N x DS0) up to a maximum of 24 concatenated time-slots for a T1/J1 link and 31 concatenated time-slots for an E1 link. Time-slots assigned to any particular channel need not be contiguous within a T1/J1 or E1 link. Unchannelised DS-3 links are assigned to a single HDLC channel.

Additionally, links may be configured independently to operate in an unframed or "clear channel" mode, in which the bit periods which are normally reserved for framing information in fact carry HDLC data. In unframed mode, links operate as unchannelised (i.e. the entire link is assigned to a single HDLC channel) regardless of link rate.

The FREEDM-84P672 supports mixing of channelised T1/J1/E1 and unchannelised or unframed links. The total number of channels in each direction is limited to 672. The maximum possible data rate over all links is 134.208 Mbps (which occurs with three DS-3 links running in unframed mode).

The FREEDM-84P672 supports three independently timed bidirectional clock/ data links, each carrying a single unchannelised HDLC stream. The links can be of arbitrary frame format and can operate at up to 52 MHz provided SYSCLK is

APPLICATION NOTE PMC-990715

**ISSUE 1**

PM7384 FREEDM-84P672

PROGRAMMER'S GUIDE

PMC-Sierra, Inc.

Extract Insert SBI C1FP C1FPOUT

RCLK[2:0] RD[2:0]

SBI PISO

SPE1\_EN SPE2\_EN SPE3\_EN

REFCLK

FASTCLK

SBI PISO

SBI PISO

SBI

DDATA[7:0] DPL DV5 DDP

SBI SIPO

SBI SIPO

AJUST\_REQ AACTIVE ADETECT[1:0]

TCLK[2:0] TD[2:0]

AV5 ADP

ADATA[7:0] APL SBI SIPO

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

running at 40 MHz. When activated, each link replaces one of the SPEs conveyed on the SBI interface. (The maximum possible data rate when all three clock/data links are activated is 156 Mbps.)

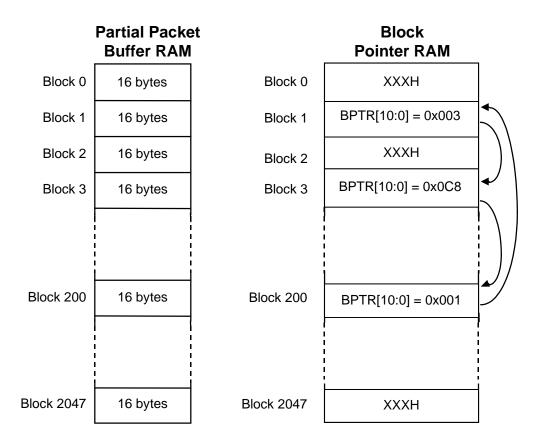

Each data stream can be HDLC processed on a channelised basis within the Receive HDLC Processor / Partial Packet Buffer (RHDL672) and Transmit HDLC Processor / Partial Packet Buffer (THDL672). There is a 32 Kbyte buffer in the RHDL672 and another 32 Kbyte buffer in the THDL672 that must be assigned to FREEDM-84P672 channels to serve as channel FIFO's. Each buffer is a group of 2048 blocks with 16 bytes per block, and a minimum of 3 blocks must be assigned to a channel during provisioning. This allows for flexible assignment of a channel FIFO based on the expected data rate for the channel.

Alternatively, the RHDL672 and THDL672 can provision a channel as transparent, in which case, the raw data stream is transferred without HDLC processing.

The FREEDM-84P672 interfaces to an embedded processor and packet memory through the PCI local bus[2]. The packet memory provides buffer locations where the receive data is written to, and where the transmit data is read from. Data is organized into packets on a per channel basis within the packet memory. The Receive DMA Controller (RMAC672), the Transmit DMA Controller (TMAC672) and the General-Purpose PCI Controller (GPIC672) blocks perform the DMA of buffer data across the PCI local bus.

Each channel provisioned within the FREEDM-84P672 contends for access to the PCI bus based on its configuration within the RMAC672 and TMAC672 blocks. This provides the designer with the flexibility to individually configure each channel to avoid receive overrun or transmit underrun, based on the channel data rate.

The PMON block provides performance monitor counts for a number of events. These counters can be read via the PCI interface and provides a means for the host software to accumulate performance statistics.

Links can be individually placed in line loopback. There is also an internal diagnostic loopback configuration for each channel which can be used to diagnose FREEDM-84P672 operation on a per channel basis.

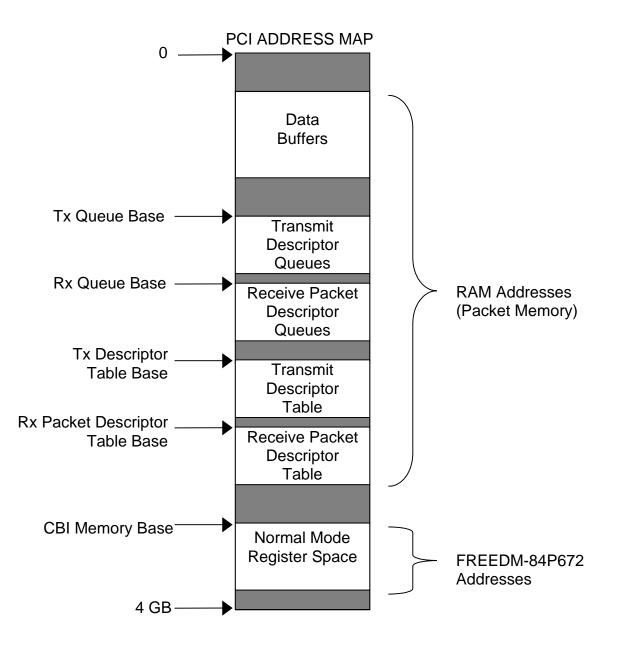

## 3.2 PCI Interface

Figure 2 shows an address map for a PCI bus which contains one FREEDM-84P672 device. These data structures are required to interface a FREEDM-

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

84P672 to the PCI bus. In this figure, PCI addresses are 32-bit physical addresses which can be observed at the address pins of the bus.

When multiple FREEDM-84P672's are attached to the bus, each FREEDM-84P672 must have a unique set of the following data structures:

• Transmit Descriptor Table

APPLICATION NOTE PMC-990715

PROGRAMMER'S GUIDE

- Receive Packet Descriptor Table

- Transmit Queue Space

- Receive Queue Space

- Normal Mode Register Space

The data structures within RAM are accessed by software running on the embedded processor, or by the FREEDM-84P672. The software must specify the location of these data structures by writing base addresses into the appropriate FREEDM-84P672 registers before activating the FREEDM-84P672.

The FREEDM-84P672 accesses RAM directly using physical addressing whereas the software may use virtual addressing. In systems which use virtual memory management, the software must translate between virtual addresses (i.e. - pointers) and physical addresses. The software must ensure that the values written to FREEDM-84P672 registers are physical addresses rather than virtual addresses. In systems that do not use virtual addressing, or in systems where virtual addresses are identical to physical addresses, no address translation is required.

The Data Buffers are written with receive data by the FREEDM-84P672, or contain transmit data which is read by the FREEDM-84P672. The descriptor tables and the queues are required to manage these buffers.

The Normal Mode Register space is accessed by the software running on the embedded processor to manage and control operation of a FREEDM-84P672 device. This register space is located in the FREEDM-84P672 and is mapped into the PCI address space by the software.

The PCI Configuration Space does not reside in the PCI address map, but it is a requirement for all PCI devices. The Configuration Space is a block of 256 contiguous bytes that reside in the PCI device, and is accessed by the embedded processor in a PCI bus Configuration Read (or Write) transaction, rather than a Memory Read (or Write) transaction. Access to this configuration space is system specific and a thorough discussion of it can be found in the PCI specification[2]. The PCI Configuration Space is discussed in section 6 of this document.

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

PROGRAMMER'S GUIDE

## 4 DATA STRUCTURES

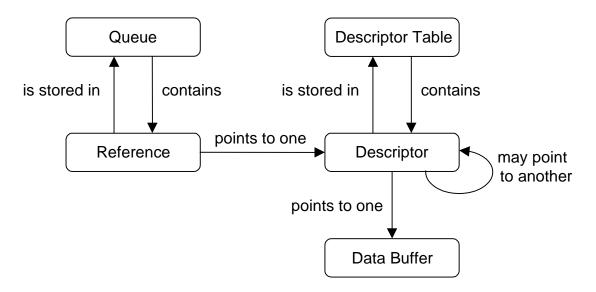

The RAM data structures accessed by the FREEDM-84P672 are descriptors, descriptor tables, references and queues. The general relationship among them is shown in Figure 3.

In this figure, the direction of the arrows refers to the direction of the relationship. For example, each reference can point to one descriptor. Also, one descriptor may point to another descriptor, thereby specifying a linked-list of descriptors.

## Figure 3 – Data Structure Relationships

These data structures are also accessed by software. The queues specify the data which may be accessed by the FREEDM-84P672 or the software, but not both simultaneously.

A Receive Packet consists of a reference pointing to one receive packet descriptor (RPD), or a linked-list of RPDs. A Transmit Packet consists of a reference pointing to one transmit descriptor (TD), or a linked-list of TDs. Transmit Packets may be linked by software, or by the FREEDM-84P672, via separate fields within each descriptor.

## 4.1 Descriptor Table

The descriptor table is essentially an array, whereby each element of the array is a descriptor and an index to the array is a reference.

**ISSUE 1**

PROGRAMMER'S GUIDE

A descriptor table holds descriptors of the same kind. The two descriptor tables are the Receive Packet Descriptor Table for receive packets, and the Transmit Descriptor Table for transmit packets.

### Allocating a Descriptor Table

A descriptor table can be located anywhere within a 32-bit address space and must be aligned on a 16 byte boundary. The memory allocation must specify a fixed memory address space that cannot be swapped or moved by the operating system.

The size of a descriptor table is specified by the software during initialization. The number of references associated with a FREEDM-84P672 determines the size of the descriptor table. The relationship is: Size (in bytes) =  $16^*$  Number of References.

The table index (reference) is a 15-bit value which limits the size to 32,768 descriptors, or 524,288 bytes. The minimum size of the descriptor table depends on the number of channels provisioned. For a descriptor table where each packet is represented by one descriptor, the number of references must be at least 3 times the number of channels provisioned. If the number of descriptors used to represent a packet is greater than one, then the number of references must increase in proportion.

The following FREEDM-84P672 registers must be written with the physical address of the Receive Descriptor Table and the Transmit Descriptor Table, respectively:

| Bit          | Register                                             |

|--------------|------------------------------------------------------|

| RPDTB[15:0]  | RMAC Packet Descriptor Table Base LSW (0x288)        |

| RPDTB[31:16] | <b>RMAC Packet Descriptor Table Base MSW</b> (0x28C) |

| TDTB[15:0]   | TMAC Transmit Descriptor Table Base LSW (0x308)      |

| TDTB[31:16]  | TMAC Transmit Descriptor Table Base MSW (0x30C)      |

**Note:** RPDTB[3:0] and TDTB[3:0] must be zero, in order to align the descriptor tables on 16 byte boundaries.

## 4.2 Receive Packet Descriptor

A Receive Packet Descriptor (RPD) is a 16 byte data structure that contains a number of fields as shown in Figure 4. RPDs are used in the receive direction to describe packets that are received and written to packet memory. Each RPD is

ISSUE 1

PROGRAMMER'S GUIDE

located in the Receive Packet Descriptor Table and is indexed from the base address using a RPD Reference (RPDR).

## Figure 4 – Receive Packet Descriptor

| Bit 31                                                                        |                                  |               |  |              |         | 0            |

|-------------------------------------------------------------------------------|----------------------------------|---------------|--|--------------|---------|--------------|

|                                                                               | Data Buffer Start Address [31:0] |               |  |              |         |              |

|                                                                               | Bytes In Buffer [15:0]           |               |  | Offset[1:0]  | CE      | Reserved (7) |

| Reserved (6)         RCC[9:0]         Res (1)         Next RPD Pointer [14:0] |                                  | ointer [14:0] |  |              |         |              |

| Reserved (16)                                                                 |                                  |               |  | Receive Buff | er Size | [15:0]       |

The following table describes the individual fields within each RPD:

| Field                              | Description                                                                                                                                                                                                                                                                                                           |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Buffer Start<br>Address[31:0] | The Data Buffer Start Address[31:0] bits point to the data buffer in host memory. This field is expected to be configured by the Host during initialisation.                                                                                                                                                          |

|                                    | The Data Buffer Start Address field is valid in all RPDs.                                                                                                                                                                                                                                                             |

| CE                                 | The Chain End (CE) bit indicates the end of a linked list of RPDs. When CE is set to logic one, the current RPD is the last RPD of a linked list of RPDs. When CE is set to logic zero, the current RPD is not the last RPD of a linked list.                                                                         |

|                                    | The CE bit is valid for all RPDs written by the RMAC672 to the Receive Ready Queue. When a packet requires only one RPD, the CE bit is set to logic one. The CE bit is ignored for all RPDs read by the RMAC672 from the Receive Free Queues, each of which is assumed to point to only one buffer, i.e. not a chain. |

| Offset[1:0]                        | The Offset[1:0] bits indicate the byte offset of the data packet from the start of the buffer. If this value is non-zero, there will be 'dummy' (i.e. undefined) bytes at the start of the data buffer prior to the packet data proper.                                                                               |

|                                    | For a linked list of RPDs, only the first RPD's Offset field<br>is valid. All other RPD Offset fields of the linked list are<br>set to 0.                                                                                                                                                                             |

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

| Field                      | Description                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Status [5:0]               | The Status[5:0] bits indicate the status of the received packet.                                                                                                                                                                                                                                                                                     |  |  |

|                            | <ul> <li>Status[0] Rx buffer overrun</li> <li>Status[1] Packet exceeds max. allowed size</li> <li>Status[2] CRC error</li> <li>Status[3] Packet Length not an exact no. of bytes</li> <li>Status[4] HDLC abort detected</li> <li>Status[5] Unused (set to 0)</li> </ul>                                                                              |  |  |

|                            | For a linked list of RPDs, only the last RPD's Status field<br>is valid. All other RPD Status fields of the linked list are<br>invalid and should be ignored. When a packet requires<br>only one RPD, the Status field is valid.                                                                                                                     |  |  |

| Bytes in Buffer<br>[15:0]  | The Bytes in Buffer[15:0] bits indicate the number of bytes<br>actually used in the current RPD's data buffer to store<br>packet data. The count excludes the 'dummy' bytes<br>inserted as a result of a non-zero Offset field. A count<br>greater than 32767 bytes indicates a packet that is<br>shorter than the expected length of the FCS field. |  |  |

|                            | The Bytes in Buffer field is invalid when Status[0] or Status[4] is asserted .                                                                                                                                                                                                                                                                       |  |  |

| Next RPD Pointer<br>[14:0] | The Next RPD Pointer[14:0] bits store a RPDR which<br>enables the RMAC672 to support linked lists of RPDs.<br>This field, which is only valid when CE is equal to logic<br>zero, contains the RPDR to the next RPD in a linked list.<br>The RMAC672 links RPDs when more than one buffer is<br>needed to store a packet.                             |  |  |

|                            | The Next RPD Pointer is not valid for the last RPD in a linked list (when CE=1). When a packet requires only one RPD, the Next RPD Pointer field is not valid.                                                                                                                                                                                       |  |  |

| RCC[9:0]                   | The Receive Channel Code (RCC[9:0]) bits are used by the RMAC672 to associate a RPD with a channel.                                                                                                                                                                                                                                                  |  |  |

|                            | For a linked list of RPDs, all the RPDs' RCC[9:0] fields are valid. i.e. all contain the same channel value.                                                                                                                                                                                                                                         |  |  |

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

| Field                         | Description                                                                                                                                                                                                                                                                                    |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Buffer Size<br>[15:0] | The Receive Buffer Size[15:0] bits indicate the size in<br>bytes of the current RPD's data buffer. This field is<br>expected to be configured by the Host during initialisation.<br>The Receive Buffer Size must be a non-zero integer<br>multiple of sixteen and less than or equal to 32752. |

|                               | The Receive Buffer Size field is valid in all RPDs.                                                                                                                                                                                                                                            |

#### Notes:

- For error checking purposes, it is recommended to examine the Bytes in Buffer[15:0] field to ensure that it does not exceed the Receive Buffer Size[15:0].

- The RPD for the FREEDM-84P672 is the same as for the FREEDM-32P672. Please see Appendix A for the differences in the RPD between the FREEDM-84P672 and the FREEDM-32.

## Receive Packet Descriptor Fields Initialized By Software

The following fields of each RPD must be assigned before writing its reference to the RPDRF Large queue, or to the RPDRF Small queue:

| Field                        | Value                                                |

|------------------------------|------------------------------------------------------|

| Data Buffer Start<br>Address | value is determined during run time or preconfigured |

| Receive Buffer Size          | value is determined during run time or preconfigured |

## **Receive Packet Descriptor Fields Modified By FREEDM-84P672**

The following fields are modified by the FREEDM-84P672 after it reads the reference from the RPDRF Large queue, or from the RPDRF Small queue, but before the same reference is written to the RPDR Ready queue:

| Field           | Value                               |  |

|-----------------|-------------------------------------|--|

| CE              | value is determined during run time |  |

| Offset          | value is determined during run time |  |

| Status          | value is determined during run time |  |

| Bytes in Buffer | value is determined during run time |  |

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE 14

PMC-Sierra, Inc.

PM7384 FREEDM-84P672

APPLICATION NOTE PMC-990715

**ISSUE 1**

PROGRAMMER'S GUIDE

| Field            | Value                               |

|------------------|-------------------------------------|

| Next RPD Pointer | value is determined during run time |

| RCC              | value is determined during run time |

#### 4.3 Transmit Descriptor

A Transmit Descriptor (TD) is a 16 byte data structure that contains a number of fields as shown in Figure 5. TDs are used in the transmit direction to describe packets that are read from packet memory and transmitted by the FREEDM-84P672. Each TD is located in the Transmit Descriptor Table and is indexed from the base address using a TD Reference (TDR).

## Figure 5 – Transmit Descriptor

| Bit | 31                                                   |  |  |  |  |       |                        | 0 |

|-----|------------------------------------------------------|--|--|--|--|-------|------------------------|---|

|     | Data Buffer Start Address [31:0]                     |  |  |  |  |       |                        |   |

|     | Bytes In Buffer [15:0] P ABT IOC CE Res (2) TCC[9:0] |  |  |  |  |       |                        |   |

| v   | V TMAC Next TD Pointer[14:0]                         |  |  |  |  | Host  | Next TD Pointer[14:0]  |   |

|     | Reserved (16)                                        |  |  |  |  | Trans | smit Buffer Size[15:0] |   |

The following table describes the individual fields within each TD:

| Field                               | Description                                                                                                                                                     |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Buffer Start<br>Address [31:0] | The Data Buffer Start Address[31:0] bits point to the data buffer in host memory.                                                                               |

|                                     | The Data Buffer Start Address field is valid in all TDs.                                                                                                        |

| Bytes In Buffer [15:0]              | The Bytes In Buffer[15:0] field is used by the host to indicate the total number of bytes to be transmitted in the current TD. Zero length buffers are illegal. |

APPLICATION NOTE PMC-990715 PMC-Sierra, Inc.

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ρ     | The Priority bit is set by the host to indicate the<br>priority of the associated packet in a two level quality<br>of service scheme. Packets with its P bit set high are<br>queued in the high priority queue in the TMAC672.<br>Packets with the P bit set low are queued in the low<br>priority queue. Packets in the low priority queue will<br>not begin transmission until the high priority queue is<br>empty.                             |

| ABT   | The Abort (ABT) bit is used by the host to abort the transmission of a packet. When ABT is set to logic 1, the packet will be aborted after all the data in the buffer has been transmitted. If ABT is set to logic 1 in the current TD, the M bit must be set low and the CE bit must be set to high.                                                                                                                                            |

| IOC   | The Interrupt On Complete (IOC) bit is used by the<br>host to instruct the TMAC672 to interrupt the host<br>when the current TD's data buffer has been read.<br>When IOC is logic 1, the TMAC672 asserts the IOCI<br>interrupt when the data buffer has been read.<br>Additionally, the Free Queue FIFO will be flushed. If<br>IOC is logic zero, the TMAC672 will not generate an<br>interrupt and the Free Queue FIFO will operate<br>normally. |

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE       | The Chain End (CE) bit is used by the host to indicate<br>the end of a linked list of TDs presented to the<br>TMAC672. The linked list can contain one or more<br>packets as delineated by the M bit (see below).<br>When CE is set to logic 1, the current TD is the last<br>TD of a linked list of TDs. When CE is set to logic 0,<br>the current TD is not the last TD of a linked list.<br>When the current TD is not the last of the linked list,<br>the Host Next TD Pointer[14:0] field is valid,<br>otherwise the field is not valid. |

|          | Note: When CE is set to logic 1, the only valid value for M is logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          | Note: When presenting raw (i.e. unpacketised) data for transmission, the host should code the M and CE bits as for a single packet chain, i.e. M=1, CE=0 for all TDs except the last in the chain and M=0, CE=1 for the last TD in the chain.                                                                                                                                                                                                                                                                                                 |

| TCC[9:0] | The Transmit Channel Code (TCC[9:0]) bits are used<br>by the host to associate a channel with a TD pointed<br>to by a TDR.                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          | All TCC[9:0] fields in a linked list of TDs must be set to the same value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V        | The V bit is used to indicate that the TMAC Next TD<br>Pointer field is valid. When set to logic 1, the TMAC<br>Next TD Pointer[14:0] field is valid. When V is set to<br>logic 0, the TMAC Next TD Pointer[14:0] field is<br>invalid. The V bit is used by the host to reclaim data<br>buffers in the event that data presented to the<br>TMAC672 is returned to the host due to a channel<br>becoming unprovisioned. The V bit is expected to be<br>initialised to logic 0 by the host.                                                     |

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

| Field                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMAC Next TD Pointer<br>[14:0] | The TMAC Next TD Pointer[14:0] bits are used to<br>store TDRs which permits the TMAC672 to create<br>linked lists of TDs passed to it via the TDRR queue.<br>The TDs are linked with other TDs belonging to the<br>same channel and same priority level. In the case<br>that data presented to the TMAC672 is returned to<br>the host due to a channel becoming unprovisioned, a<br>TDR pointing to the start of the per-channel linked list<br>of TDs is placed on the TDRF queue. It is the<br>responsibility of the host to follow the TMAC672 and<br>host links in order to recover all the buffers. |

| Μ                              | The More (M) bit is used by the host to support<br>packets that require multiple TDs. If M is set to<br>logic 1, the current TD is just one of several TDs for<br>the current packet. If M is set to logic 0, this TD<br>either describes the entire packet (in the single TD<br>packet case) or describes the end of a packet (in the<br>multiple TD packet case).                                                                                                                                                                                                                                      |

|                                | Note: When M is set to logic 1, the only valid value for CE is logic 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Host Next TD Pointer<br>[14:0] | The Host Next TD Pointer[14:0] bits are used to store<br>TDRs which permits the host to support linked lists of<br>TDs. As described above, linked lists of TDs are<br>terminated by setting the CE bit to logic 1. Linked<br>lists of TDs are used by the host to pass multiple TD<br>packets or multiple packets associated with the same<br>channel and priority level to the TMAC672.                                                                                                                                                                                                                |

| Transmit Buffer Size<br>[15:0] | The Transmit Buffer Size[15:0] field is used to<br>indicate the size in bytes of the current TD's data<br>buffer. (N.B. The TMAC672 does not make use of<br>this field.)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

**Note:** The TD for the FREEDM-84P672 is the same as for the FREEDM-32P672. Please see Appendix B for the differences in the TD between the FREEDM-84P672 and the FREEDM-32.

## Transmit Descriptor Fields Initialized By Software

The following fields of a TD (or a linked-list of TDs) must be assigned before writing its reference to the TDR Ready queue:

| Field                        | Value                                                |

|------------------------------|------------------------------------------------------|

| Data Buffer Start<br>Address | value is determined during run time or preconfigured |

| Bytes In Buffer              | value is determined during run time or preconfigured |

| Р                            | value is determined during run time or preconfigured |

| ABT                          | value is determined during run time or preconfigured |

| IOC                          | value is determined during run time or preconfigured |

| CE                           | value is determined during run time or preconfigured |

| ТСС                          | value is determined during run time or preconfigured |

| V                            | 0                                                    |

| Μ                            | value is determined during run time or preconfigured |

| Host Next TD Pointer         | value is determined during run time or preconfigured |

## Transmit Descriptor Fields Modified By FREEDM-84P672

The following fields may be modified by the FREEDM-84P672 after it reads the reference from the TDR Ready queue, but before the same reference is written to the TDR Free queue:

| Field                | Value                               |

|----------------------|-------------------------------------|

| V                    | value is determined during run time |

| TMAC Next TD Pointer | value is determined during run time |

## 4.4 Data Buffers

In the receive path, the FREEDM-84P672 writes receive packet data into data buffers. In the transmit path, the FREEDM-84P672 reads transmit packet data

PROGRAMMER'S GUIDE

from data buffers. A buffer must be allocated and assigned to each descriptor by the software.

## Allocation of Data Buffers

Buffers must be allocated in fixed memory. The receive data buffer size must be a non-zero integer multiple of 16 bytes, with a maximum size of 32,752 bytes and a minimum size of 16 bytes. There is no restriction for the address alignment of the buffers.

For a receive buffer, the following fields of a RPD must be assigned:

| Field                        | Value                                                |

|------------------------------|------------------------------------------------------|

| Data Buffer Start<br>Address | value is determined during run time or preconfigured |

| Receive Buffer Size          | value is determined during run time or preconfigured |

For a transmit buffer, the following fields of a TD must be assigned:

| Field                        | Value                                                |

|------------------------------|------------------------------------------------------|

| Data Buffer Start<br>Address | value is determined during run time or preconfigured |

| Bytes In Buffer              | value is determined during run time or preconfigured |

The FREEDM-84P672 automatically links RPDs when the receive packet length exceeds the buffer size.

The software must link TDs when the packet data is "scattered" among a number of buffers.

## 4.5 References

References are dword structures used to access descriptors within a descriptor table. They also have status bits which are written by the FREEDM-84P672 after it has processed the packet. The reference, including status bits, is written into a queue by the FREEDM-84P672 during a queue write operation. The status bits indicate the success of receive or transmit processing and should be checked by software when the reference is read from the queue.

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

PROGRAMMER'S GUIDE

### 4.5.1 Receive Packet Descriptor Reference

Each Receive Packet Descriptor Reference (RPDR) Ready Queue element is 32 bits in size, but only the least significant 17 bits are valid. The 17 least significant bits consist of a 15-bit RPDR and 2 status bits for the RPD pointed at by this RPDR. A RPDR has the following fields:

| Bit 31 |        | 17 | 16 15       | 14         | 0 |

|--------|--------|----|-------------|------------|---|

|        | UNUSED |    | STATUS[1:0] | RPDR[14:0] |   |

| Field       | Description                                                                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATUS[1:0] | <ul> <li>The encoding for the status field is as follows:</li> <li>00 – Successful reception of packet.</li> <li>01 – Unsuccessful reception of packet.</li> <li>10 – Unprovisioned partial packet.</li> <li>11 – Partial packet returned due to RAWMAX limit being reached.</li> </ul> |

| RPDR[14:0]  | The RPDR[14:0] field defines the offset of the first RPD in a linked chain of RPDs, each pointing to a buffer containing the received data.                                                                                                                                             |

When the RMAC672 writes a STATUS+RPDR to the RPDR Ready queue, it sets bits [23:17] of the queue element to all 0's and leaves bits [31:24] unmodified as follows:

| Bit 31 | 24     | 23 17     | 16 15       | 14         | 0 |

|--------|--------|-----------|-------------|------------|---|

| UNMO   | DIFIED | 000 0000B | STATUS[1:0] | RPDR[14:0] |   |

This may be useful to software which polls host memory to determine when a reference has been written into a queue, instead of responding to an interrupt and reading a FREEDM-84P672 register. The software should write a non-zero value to bits [23:17] after reading the reference, and at a later time it can check whether the non-zero value was overwritten by the FREEDM-84P672, indicating that the FREEDM-84P672 has written another reference into this queue location.

PM7384 FREEDM-84P672

PROGRAMMER'S GUIDE

**Note:** Only one RPDR is written into the RPDR Ready queue per receive packet, and this RPDR represents the linked list of RPDs which identify the receive packet.

## 4.5.2 Transmit Descriptor Reference

Each Transmit Descriptor Reference (TDR) Free Queue element is 32 bits in size, but only the least significant 18 bits are valid. The 18 least significant bits consist of a 15-bit TDR and 3 status bits for the TD pointed at by this TDR. A TDR has the following fields:

| Bit 31 |        | 18 | 17 15       | 14        | 0 |

|--------|--------|----|-------------|-----------|---|

|        | UNUSED |    | STATUS[2:0] | TDR[14:0] |   |

| Field       | Description                                                                                                      | Description                                                                                                                                                                                                     |  |

|-------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Status[2:0] | The TMAC672 fills in the Status field to indicate to the host the results of processing the TD. The encoding is: |                                                                                                                                                                                                                 |  |

|             | Status[1:0]                                                                                                      | Description                                                                                                                                                                                                     |  |

|             | 00<br>01<br>10<br>11                                                                                             | Last or only buffer of packet, buffer read.<br>Buffer of partial packet, buffer read.<br>Unprovisioned channel, buffer not read.<br>Malformed packet (e.g. Bytes In Buffer field<br>set to 0), buffer not read. |  |

|             | Status[2]                                                                                                        | Description                                                                                                                                                                                                     |  |

|             | 0<br>1                                                                                                           | No underflow detected.<br>Underflow detected.                                                                                                                                                                   |  |

| TDR[14:0]   | The TDR[14 returned.                                                                                             | :0] field contains the offset of the TD                                                                                                                                                                         |  |

When the TMAC672 writes a STATUS+TDR into the TDR Free queue, it sets bits [23:18] of the queue element to all 0's and leaves bits [31:24] unmodified as follows:

| Bit 31 | 24     | 23     | 18 17  | 15      | 14        | 0 |

|--------|--------|--------|--------|---------|-----------|---|

| UNMO   | DIFIED | 00 000 | B STAT | US[2:0] | TDR[14:0] |   |

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

This may be useful to software which polls host memory to determine when a reference has been written into a queue, instead of responding to an interrupt and reading a FREEDM-84P672 register. The software should write a non-zero value to bits [23:18] after reading the reference, and at a later time it can check whether the non-zero value was overwritten by the FREEDM-84P672, indicating that the FREEDM-84P672 has written another reference into this queue location.

#### Notes:

- The TDR associated with each TD of a transmit packet is written to the TDR Free queue. In the case of a packet with multiple TDs there will be multiple TDRs written to the TDR Free queue.

- The Status<sup>[2]</sup> field of a TDR can be used to identify the occurrence of an • underflow condition on the channel associated with the TDR. The underflow may or may not have occurred on the buffer associated with the TDR read from the TDR Free queue.

### 4.5.3 Access to Descriptors

TDs or RPDs can be accessed using the index field of the reference and the base address of the descriptor table as illustrated by the pseudo code below:

```

/* Need to mask out the upper 17 bits of the descriptor reference to

* extract the index field. */

#define

RPD INDEX MASK

0x00007FFF

#define

TD INDEX MASK RPD INDEX MASK

#define MUL_16_BYTES

4

index = RxReference & RPD INDEX MASK;

/* The address of the descriptor in the descriptor table

* can be determined as shown below */

desc_addr = desc_table_base_addr + (index << MUL_16_BYTES);</pre>

```

#### 4.6 Queues

A queue is a FIFO buffer located in fixed memory that holds a number of references. The FREEDM-84P672 has 5 gueues which must be allocated. There are 2 queues for TDRs and 3 queues for RPDRs. The software must allocate memory for each of these queues.

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

In the receive direction, there is the Receive Packet Descriptor Reference Free Small queue (RPDR Free Small queue), the Receive Packet Descriptor Reference Free Large queue (RPDR Free Large queue), and the Receive Packet Descriptor Reference Ready queue (RPDR Ready queue). The FREEDM-84P672 reads from the RPDR Free Small queue and the RPDR Free Large queue to get free buffers into which the receive data is written. When the receive operation is complete, the FREEDM-84P672 writes a RPDR to the RPDR Ready queue. The software reads from the RPDR Ready queue to process a receive packet, and it writes to the RPDR Free Small (or Large) queue to reuse the RPD for another packet.

The FREEDM-84P672 obtains free buffers from the RPDR Free Small (or Large) queue based on the following 2-step algorithm:

- 1. The first buffer into which the receive packet is written is obtained from the RPDR Free Small queue, and if this queue is empty it is obtained from the RPDR Free Large queue.

- If the receive packet length exceeds the small buffer size then the additional receive data is written into buffers obtained from the RPDR Free Large queue. If the RPDR Free Large queue is empty then the additional buffers are obtained from the RPDR Free Small queue.

In the transmit direction, there is the Transmit Descriptor Reference Ready queue (TDR Ready queue) and the Transmit Descriptor Reference Free queue (TDR Free queue). The software writes a TDR to the TDR Ready queue when it wants the FREEDM-84P672 to transmit a packet. The FREEDM-84P672 reads from the TDR ready queue and starts to transmit the packet, and when it has completed the transmit operation, it writes the TDR to the TDR Free queue. The software reads from the TDR Free queue to confirm that the packet has been transmitted, and to reuse the TD for another packet.

| Queue           | Read By       | Written By    |

|-----------------|---------------|---------------|

| RPDR Free Large | FREEDM-84P672 | Software      |

| RPDR Free Small | FREEDM-84P672 | Software      |

| RPDR Ready      | Software      | FREEDM-84P672 |

| TDR Free        | Software      | FREEDM-84P672 |

| TDR Ready       | FREEDM-84P672 | Software      |

The entity (either the software or the FREEDM-84P672) which reads from a queue and the entity which writes to a queue is as follows:

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

There are four indexes for each queue that are used to manage its state. These indexes are located in the FREEDM-84P672 Normal Mode Register space. The values are described as follows:

| Index | Description                                                                                                                                                                                        |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| start | The start index marks the lowest address of the queue. This is<br>the first location in the queue. This value should not be<br>modified after initialization.                                      |  |  |

| write | The write index is modified by the entity which writes to the queue. The write index marks the address where a reference can be written. After the reference is written this value is incremented. |  |  |

| read  | The read index is modified by the entity which reads from the queue. The read index marks the last location accessed by the reading entity. After the reference is read this value is incremented. |  |  |

| end   | The end index marks the address which follows the last<br>location (the highest addressable location) in the queue. This<br>value should not be modified after initialization.                     |  |  |

**Note:** The end index points to a location that is beyond the queue; a reference can not be read from or written to this location. However, the start index of one queue can be set to the end index of another queue.

The various queue entities (references) in Figures 6 to 8 are illustrated using the following legend:

| Empty Reference Location                  |  |

|-------------------------------------------|--|

| Valid Reference Location                  |  |

| Invalid Reference Location for this Queue |  |

Some normal queue states are illustrated in Figure 6. Note the circular nature of the queues.

APPLICATION NOTE PMC-990715

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

## Figure 6 – Normal Queue States

The empty queue states are illustrated in Figure 7. The queue is empty when the read index is one location before the write index, or when the read index is one location before the end index and the write index equals the start index.

## Figure 7 – Empty Queue States

The full queue states are illustrated in Figure 8. The queue is full when the read index is equal to the write index.

APPLICATION NOTE PMC-990715 PMC-Sierra, Inc.

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

### Figure 8 – Full Queue States

#### **Allocation of Queues**

From Figure 8, it can be seen that the physical size of a queue is one dword larger than the number of references in the queue when it is full. Therefore in order to create a queue that holds 128 references, the software must allocate contiguous memory of 129 dwords.

To obtain the best possible bus utilization, the size of a queue should not be too small, as this would lead to more frequent accesses to the read and/or write index registers of the FREEDM-84P672. The minimum recommended queue

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

size is approximately 32 references. In general, the queue should be large enough to hold one reference per provisioned channel.

The queues used for receive packets are located in fixed memory as offsets from a base address. The queues used for transmit packets are located in fixed memory as offsets from another base address. Base addresses must be dword aligned and are programmed as follows for the receive direction and transmit direction, respectively:

| Bits       | Register                             |

|------------|--------------------------------------|

| RQB[15:0]  | RMAC Receive Queue Base LSW (0x290)  |

| RQB[31:16] | RMAC Receive Queue Base MSW (0x294)  |

| TQB[15:0]  | TMAC Transmit Queue Base LSW (0x310) |

| TQB[31:16] | TMAC Transmit Queue Base MSW (0x314) |

The RPDR Free Large queue, the RPDR Free Small queue and the RPDR Ready queue must reside within 256Kbytes of the RMAC672 Receive Queue Base address. The size of each queue is specified by assignment of the start, write, read and end indexes.

The TDR Ready queue and the TDR Free queue must reside within 256Kbytes of the TMAC672 Transmit Queue Base address. The size of each queue is specified by assignment of the start, write, read and end indexes.

## **Initialization of Queues**

The software must initialize each queue after the allocation procedure. Normally, a queue is initialized with the state shown below:

| Queue           | Initial State |

|-----------------|---------------|

| RPDR Free Large | Full          |

| RPDR Free Small | Full          |

| RPDR Ready      | Empty         |

| TDR Free        | Empty         |

| TDR Ready       | Empty         |

The software must write valid RPD References into the RPDRF Small (and Large) queues. The software may force the RMAC672 to store received data in buffers of only one size by setting one of the receive free queues to zero length

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

(i.e. – by setting the start and end index registers of one of the queues to equal values).

The software must also write the following FREEDM-84P672 registers with valid indexes:

| Bits           | Register                                                                                |

|----------------|-----------------------------------------------------------------------------------------|

| RPDRLFQS[15:0] | RMAC Packet Descriptor Reference Large Buffer<br>Free Queue Start (0x298)               |

| RPDRLFQW[15:0] | <b>RMAC Packet Descriptor Reference Large Buffer</b><br><b>Free Queue Write</b> (0x29C) |

| RPDRLFQR[15:0] | <b>RMAC Packet Descriptor Reference Large Buffer</b><br><b>Free Queue Read</b> (0x2A0)  |

| RPDRLFQE[15:0] | RMAC Packet Descriptor Reference Large Buffer<br>Free Queue End (0x2A4)                 |

| RPDRSFQS[15:0] | RMAC Packet Descriptor Reference Small Buffer<br>Free Queue Start (0x2A8)               |

| RPDRSFQW[15:0] | <b>RMAC Packet Descriptor Reference Small Buffer</b><br><b>Free Queue Write</b> (0x2AC) |

| RPDRSFQR[15:0] | RMAC Packet Descriptor Reference Small Buffer<br>Free Queue Read (0x2B0)                |

| RPDRSFQE[15:0] | <b>RMAC Packet Descriptor Reference Small Buffer</b><br><b>Free Queue End</b> (0x2B4)   |

| RPDRRQS[15:0]  | <b>RMAC Packet Descriptor Reference Ready Queue</b><br><b>Start</b> (0x2B8)             |

| RPDRRQW[15:0]  | <b>RMAC Packet Descriptor Reference Ready Queue</b><br>Write (0x2BC)                    |

| RPDRRQR15:0]   | <b>RMAC Packet Descriptor Reference Ready Queue</b><br><b>Read</b> (0x2C0)              |

| RPDRRQE[15:0]  | <b>RMAC Packet Descriptor Reference Ready Queue</b><br><b>End</b> (0x2C4)               |

| TDRFQS[15:0]   | <b>TMAC Transmit Descriptor Reference Free Queue</b><br><b>Start</b> (0x318)            |

| TDRFQW[15:0]   | <b>TMAC Transmit Descriptor Reference Free Queue</b><br>Write (0x31C)                   |

| TDRFQR[15:0]   | TMAC Transmit Descriptor Reference Free Queue Read (0x320)                              |

PMC-990715

APPLICATION NOTE

PM7384 FREEDM-84P672

ISSUE 1

PROGRAMMER'S GUIDE

| Bits         | Register                                                                      |

|--------------|-------------------------------------------------------------------------------|

| TDRFQE[15:0] | <b>TMAC Transmit Descriptor Reference Free Queue</b><br><b>End</b> (0x324)    |

| TDRRQS[15:0] | <b>TMAC Transmit Descriptor Reference Ready Queue</b><br><b>Start</b> (0x328) |

| TDRRQW[15:0] | <b>TMAC Transmit Descriptor Reference Ready Queue</b><br>Write (0x32C)        |

| TDRRQR[15:0] | <b>TMAC Transmit Descriptor Reference Ready Queue</b><br><b>Read</b> (0x330)  |

| TDRRQE[15:0] | <b>TMAC Transmit Descriptor Reference Ready Queue</b><br><b>End</b> (0x334)   |

#### **Queue Operation**

The following code illustrates how the software can access a queue. It should be noted for a specific queue that the software will only read from it or write to it, but not both read and write to it.

```

#define QUEUE_BATCH_SIZE

6

#define READ_INDEX_REGISTER(address)

((*address)&0xFFFF)

#define WRITE_INDEX_REGISTER(address,value)

*address = (dword) value

BOOL ReadQueue(dword* pReference)

{

dword* pQueueElement;

/* The following code segment ensures the write index register

* is not read too frequently. Thereby, minimizing

* utilization of the PCI bus. */

if (Headroom == 0) {

/* Headroom was initialized to zero, and must be reinitialized

* to a non-zero value in the following code segment before

* the software is able to read a reference from the queue.

* The Headroom is the number of references in the queue when the

* write index was last read by software, minus the number of

* these references that have been read. */

Write = READ_INDEX_REGISTER(pWriteRegister);

if (Write <= Read)

Headroom = Write - Start + End - Read - 1;

else

Headroom = Write - Read - 1;

```

PM7384 FREEDM-84P672

```

APPLICATION NOTE

PMC-990715

```

}

{

**ISSUE 1**

PROGRAMMER'S GUIDE

```

/* Exit if the queue is empty */

if (Headroom == 0) return FALSE;

}

Headroom--;

/* Determine the read index of the reference in the queue.

* Reading is a pre-increment operation. */

Read++;

if (Read == End)

Read = Start;

/* Read the reference from a RAM location */

pQueueElement = pQueueBaseAddress + Read;

*pReference = *pQueueElement;

/* The following code segment ensures the read index register

* is not written too frequently. Thereby, minimizing

* utilization of the PCI bus. */

if (CacheSize-- == 0) {

WRITE_INDEX_REGISTER(pReadRegister, Read);

CacheSize = QUEUE_BATCH_SIZE;

}

return TRUE;

BOOL WriteQueue(dword Reference)

dword* pQueueElement;

/* The following code segment ensures the read index register

* is not read too frequently. Thereby, minimizing

* utilization of the PCI bus. */

if (Headroom == 0) {

/* Headroom was initialized to zero, and must be reinitialized

* to a non-zero value in the following code segment before

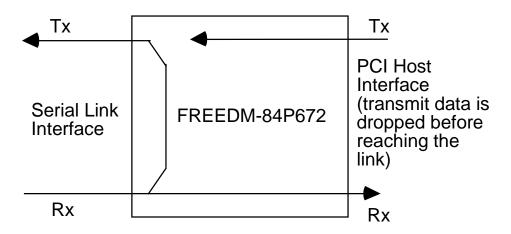

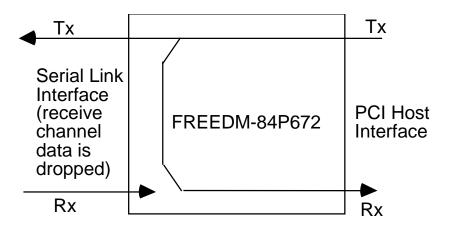

* the software is able to write a reference from the queue.